## International Workshop on Embedded Artificial Intelligence Devices, Systems, and Industrial Applications (EAI)

ECSEL JL

Milan, Italy 19 September 2022

International Workshop on Embedded Artificial Intelligence Devices, Systems, and Industrial Applications (EAI)

Low-Power Vertically Stacked One Time Programmable Multi-bit IGZO-Based BEOL Compatible Ferroelectric TFT Memory Devices with Lifelong Retention for Monolithic 3D-Inference Engine Applications

19 September 2022 Milan, Italy

- Introduction

- Process flow

- Capacitor Characterization

- Transistor Characterization

- Implications to Neural Network

- Benchmarking

3

#### Introduction

- Process flow

- Capacitor Characterization

- Transistor Characterization

- Implications to Neural Network

- Benchmarking

#### Introduction

#### Introduction

- Introduction

- Process flow

- Capacitor Characterization

- Transistor Characterization

- Implications to Neural Network

- Benchmarking

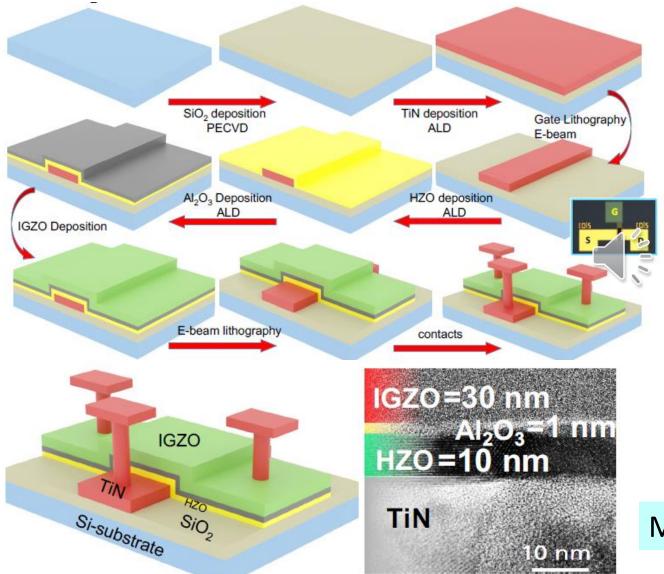

#### **Process flow**

Standard cleaning of Si wafer Deposition of SiO<sub>2</sub> by PECVD Deposition of TiN by ALD Gate lithography by E-beam Deposition of HZO by ALD Deposition of Al<sub>2</sub>O<sub>3</sub> by ALD **Deposition of IGZO** E-beam lithography Contact pad deposition.

Maximum process temperature is 350°C

- Introduction

- Process flow

- Capacitor Characterization

- Transistor Characterization

- Implications to Neural Network

- Benchmarking

## **Capacitor Characterization**

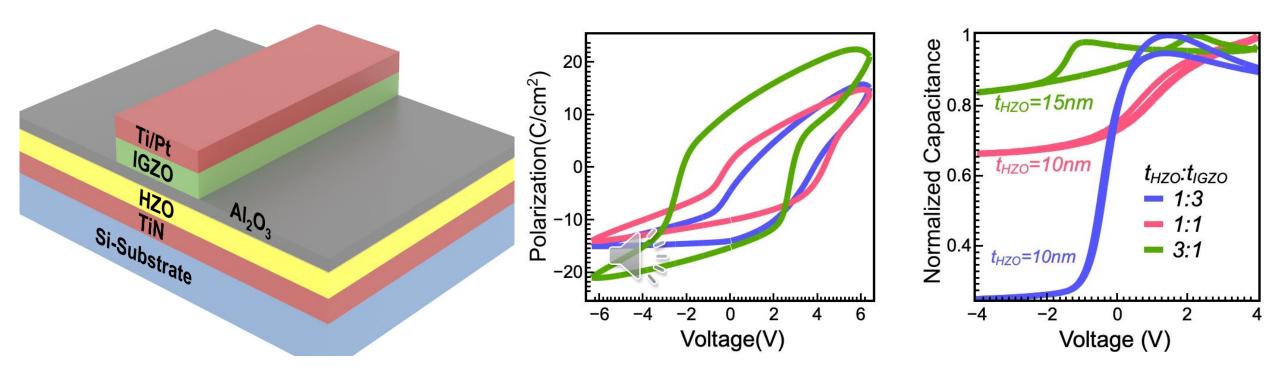

Schematic of the gate-stack with IGZO as semiconductor and HZO as a ferroelectric layer.

Polarization versus voltage (P–V) response of metal-semiconductor-FE-metal (MSFM) gate stacks with various thicknesses of the HZO and IGZO.

Capacitance versus voltage (C–V) response of metal-semiconductor-FE-metal (MSFM) gate stacks with various thicknesses of the HZO and IGZO.

- Introduction

- Process flow

- Capacitor Characterization

- Transistor Characterization

- Implications to Neural Network

- Benchmarking

#### **Transistor Characterization**

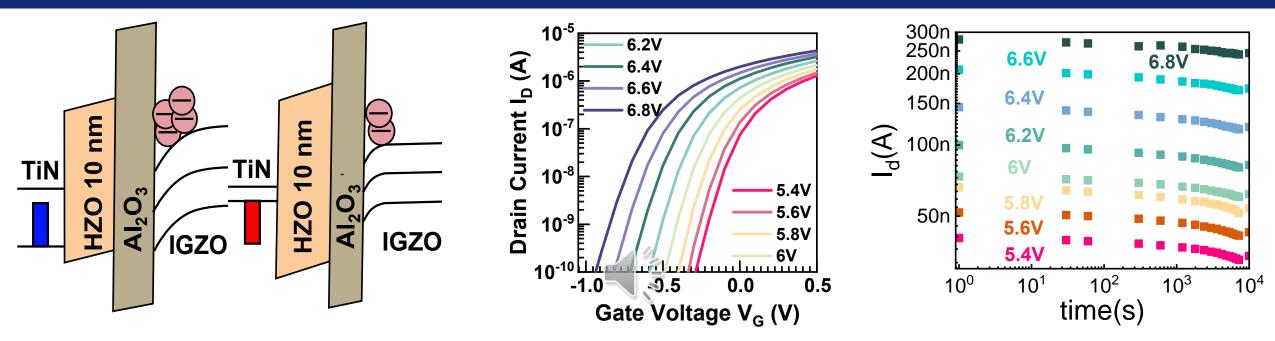

- > The band diagram of the IGZO-MOS capacitor during the program and erase operation. Although the high value of  $\mu_n$  facilitates fast programming, the low value of  $\mu_p$  inhibits the erase operation by preventing the supply of holes during erase operation.

- ➤ 3 bits/ cell WRITE operation in IGZO-based FeTFTs with 200 ns wide pulses of minimum amplitude 5.2 V and maximum amplitude of 6.8 V.

- The measured retention characteristics show stable retention of 8-states for 10<sup>4</sup> seconds and for ten years for 2bits/cell operation with negligible degradation.

- Introduction

- Process flow

- Capacitor Characterization

- Transistor Characterization

- Implications to Neural Network

- Benchmarking

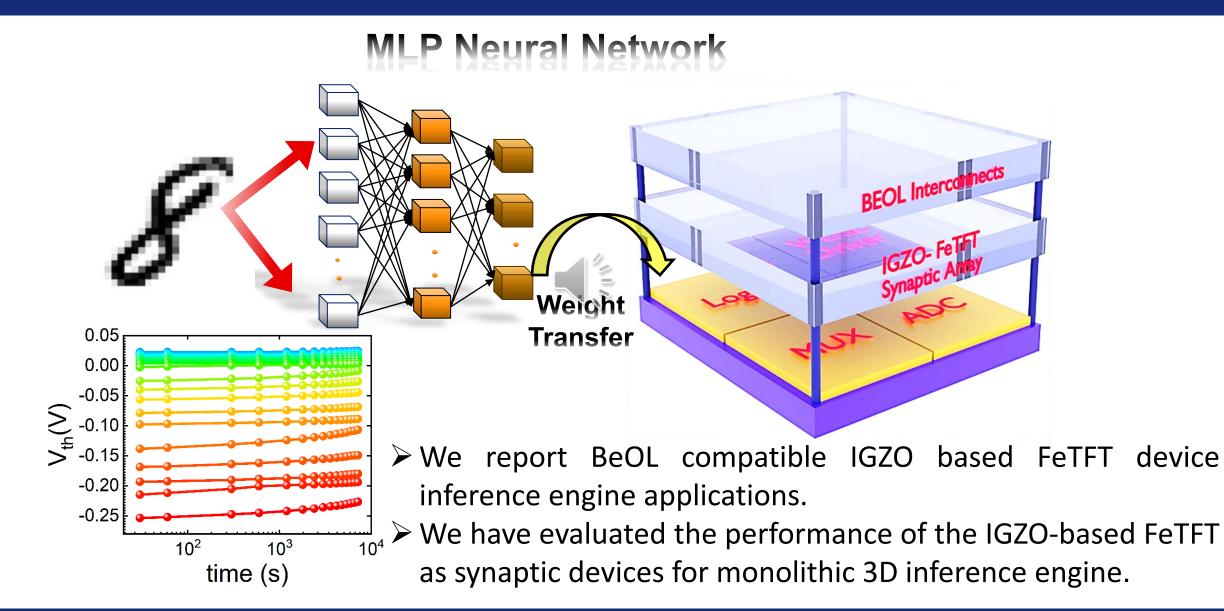

## Implications to Neural Network

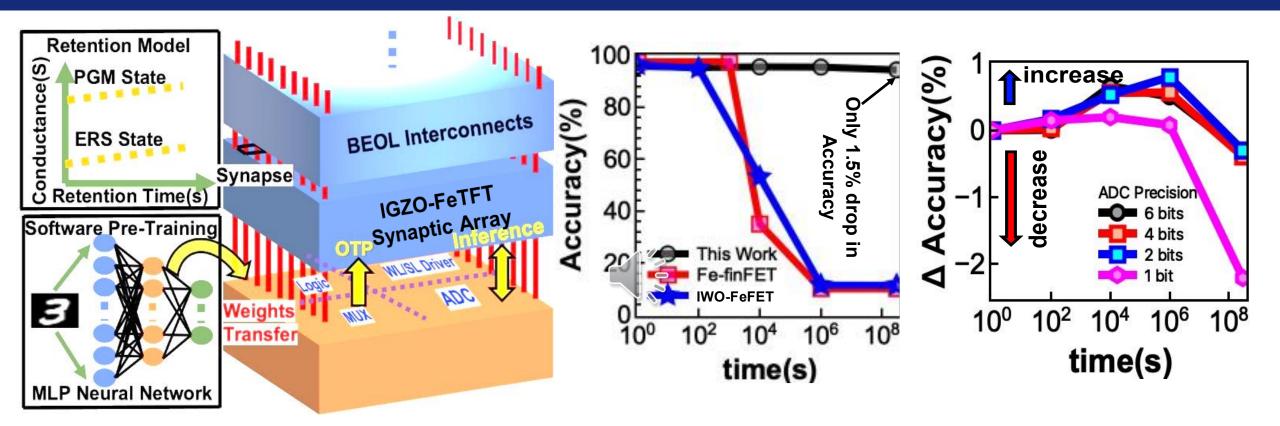

- > The modus operandi of monolithic 3D inference engine based on multilayer perceptron neural network.

- The reported inference engine shows life-long lossless inference operation and (c). Reducing the ADC precision to 1bit causes a mere accuracy degradation of 1.87% from FP precision.

- > 1-bit ADC shows less than 2% accuracy loss over 10 years.

- Introduction

- Process flow

- Capacitor Characterization

- Transistor Characterization

- Implications to Neural Network

- Benchmarking

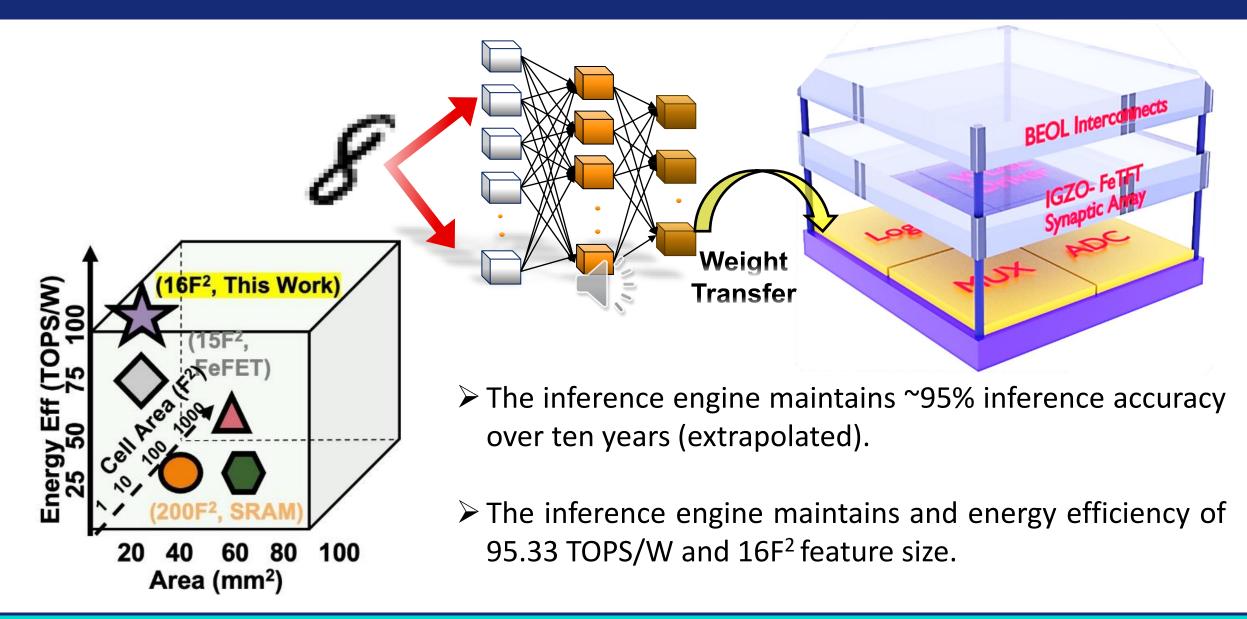

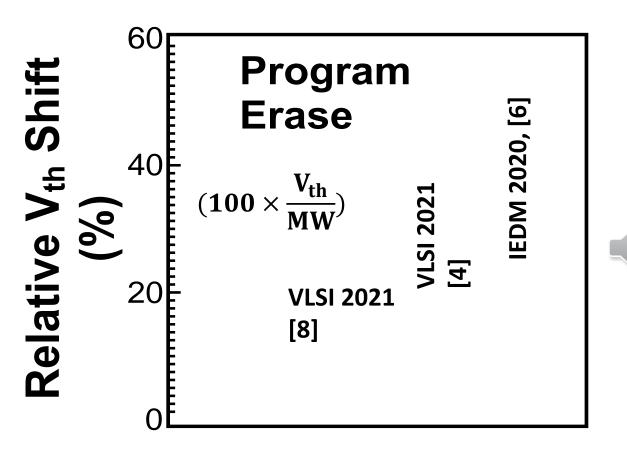

### Benchmarking

| Device Type                          | Fe-FinFET<br>[9] | IWO-FeFET<br>[14] | This Work         |

|--------------------------------------|------------------|-------------------|-------------------|

| M3D Integrator                       | No               | Yes               | Yes               |

| Cell Area (F <sup>2</sup> )          | 15F <sup>2</sup> | 15F <sup>2</sup>  | 16F <sup>2</sup>  |

|                                      | 100K             | 4M                | 100M              |

| MW @10 years                         | 1                | 0.2               | 1                 |

| Inference Accuracy<br>Drop @10 years | ~85%             | 85%               | 1.5%              |

| Energy Efficiency<br>(TOPS/W)        | N/A              | 71.04             | 95.33<br>(Binary) |

This research was funded by the ECSEL Joint Undertaking project ANDANTE and TEMPO.

We thank Dr. Hoang-Hiep Le and Prof. Darsen Lu from National Cheng Kung University for helping us with the neuromorphic simulations.

#### References

- 1. T. Ali *et al.*, "A Multilevel FeFET Memory Device based on Laminated HSO and HZO Ferroelectric Layers for High-Density Storage," 2019 IEEE International Electron Devices Meeting (IEDM), 2019, pp. 28.7.1-28.7.4, doi: https://doi.org/10.1109/IEDM19573.2019.8993642

- 2. Kim, M.-K., & Lee, J.-S. (2019). Ferroelectric Analog Synaptic Transistors. Nano Letters, 19(3), 2044–2050. <u>https://doi.org/10.1021/acs.nanolett.9b00180</u>.

- 3. Kim, D., Jeon, Y.-R., Ku, B., Chung, C., Kim, T. H., Yang, S., Won, U., Jeong, T., & Choi, C. (2021). Analog Synaptic Transistor with Al-Doped HfO 2 Ferroelectric Thin Film. ACS Applied Materials & Interfaces, 13(44), 52743–52753. https://doi.org/10.1021/acsami.1c12735

- 4. Soliman, T., Gmbh, R. B., Laleni, N., & Ipms, F. (2022). FELIX : A Ferroelectric FET Based Low Power Mixed-Signal In-Memory Architecture for DNN Acceleration. ACM Transactions on Embedded Computing Systems. <a href="https://doi.org/10.1145/3529760">https://doi.org/10.1145/3529760</a>.

- 5. Trentzsch, M., Flachowsky, S., Richter, R., Paul, J., Reimer, B., Utess, D., Jansen, S., Mulaosmanovic, H., Muller, S., Slesazeck, S., Ocker, J., Noack, M., Muller, J., Polakowski, P., Schreiter, J., Beyer, S., Mikolajick, T., & Rice, B. (2017). A 28nm HKMG super low power embedded NVM technology based on ferroelectric FETs. *Technical Digest - International Electron Devices Meeting*, *IEDM*. <u>https://doi.org/10.1109/IEDM.2016.7838397</u>

- 6. Wang, P., & Yu, S. (2020). Ferroelectric devices and circuits for neuro- inspired computing. MRS Communications, 10(4). https://doi.org/10.1557/mrc.2020.71

- 7. S. De et al., "READ-Optimized 28nm HKMG Multibit FeFET Synapses for Inference-Engine Applications," in IEEE Journal of the Electron Devices Society, vol. 10, pp. 637-641, 2022, doi: 10.1109/JEDS.2022.3195119

- 8. De S, Baig MA, Qiu B-H, Müller F, Le H-H, Lederer M, Kämpfe T, Ali T, Sung P-J, Su C-J, Lee Y-J and Lu DD (2022) Random and Systematic Variation in Nanoscale Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> Ferroelectric FinFETs: Physical Origin and Neuromorphic Circuit Implications. *Front. Nanotechnol.* 3:826232. doi: 10.3389/fnano.2021.826232.

- 9. S. De, D. D. Lu, H.-H. Le, S. Mazumder, Y.-J. Lee, W.-C. Tseng, B.-H. Qiu, Md. A. Baig, P.-J. Sung, C.-J. Su, C.-T. Wu, W.-F. Wu, W.-K Yeh, Y.-H. Wang, "Ultra-low power robust 3bit/cell Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric finFET with high endurance for advanced computing-in-memory technology," in *Proc. Symp. VLSI Technology, 2021*.

- 10. S. De, H.H.Le, B.H.Qiu, M.A.Baig, P.J.Sung, C.J.Su, Y.J.Lee and D.D.Lu, "Robust Binary Neural Network Operation From 233 K to 398 K via Gate Stack and Bias Optimization of Ferroelectric FinFET Synapses," in *IEEE Electron Device Letters*, vol. 42, no. 8, pp. 1144- 1147, Aug. 2021, doi: <u>https://doi.org/10.1109/LED.2021.3089621.</u>

- 11. S. De, M. A. Baig, B. -H. Qiu, H. -H. Le, Y. -J. Lee and D. Lu, "Neuromorphic Computing with Fe-FinFETs in the Presence of Variation," 2022 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), 2022, pp. 1-2, doi: 10.1109/VLSI-TSA54299.2022.9771015.

- 12. De, S., Qiu, B.-H., Bu, W.-X., Baig, Md. A., Su, C.-J., Lee, Y.-J., & Lu, D. D. (2021). Neuromorphic Computing with Deeply Scaled Ferroelectric FinFET in Presence of Process Variation, Device Aging and Flicker Noise. *CoRR*, *abs/2103.13302*. <u>https://arxiv.org/abs/2103.13302</u>

- 13. C. Matsui, K. Toprasertpong, S. Takagi and K. Takeuchi, "Energy- Efficient Reliable HZO FeFET Computation-in-Memory with Local Multiply & Global Accumulate Array for Source-Follower & Charge-Sharing Voltage Sensing," 2021 Symposium on VLSI Circuits, 2021, pp. 1-2, doi: 10.23919/VLSICircuits52068.2021.9492448.

- 14. S. Dutta *et al.*, "Monolithic 3D Integration of High Endurance Multi-Bit Ferroelectric FET for Accelerating Compute-In-Memory," *2020 IEEE International Electron Devices Meeting (IEDM)*, 2020, pp. 36.4.1-36.4.4, doi: 10.1109/IEDM13553.2020.9371974.

- 15. Lehninger, D., Ellinger, M., Ali, T., Li, S., Mertens, K., Lederer, M., Olivio, R., Kämpfe, T., Hanisch, N., Biedermann, K., Rudolph, M., Brackmann, V., Sanctis, S., Jank, M. P. M., Seidel, K., A Fully Integrated Ferroelectric Thin-Film-Transistor – Influence of Device Scaling on Threshold Voltage Compensation in Displays. *Adv. Electron. Mater.* 2021, 7, 2100082. <u>https://doi.org/10.1002/aelm.202100082</u>

#### **Event Organisers**

The TEMPO project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826655. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Belgium, France, Germany, The Netherlands, Switzerland. www.tempo-ecsel.eu

The Key Digital Technologies Joint Undertaking - the Public-Private Partnership for research, development and innovation – funds projects for assuring worldclass expertise in these key enabling technologies, essential for Europe's

competitive leadership in the era of the digital economy. KDT JU is the successor

The AI4DI project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826060. The JU receives support from the European Union's Horizon 2020 research and innovation programme and the national

to the ECSEL JU programme. www.kdt-ju.europa.eu

authorities. www.ai4di.eu

The ANDANTE project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 876925. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Belgium, France, Germany, The Netherlands, Portugal, Spain, Switzerland. <u>www.andante-ai.eu</u>

# Thank You For your attention

Copyright © 2022