## International Workshop on Embedded Artificial Intelligence Devices, Systems, and Industrial Applications (EAI)

ECSEL JL

Milan, Italy 19 September 2022

International Workshop on Embedded Artificial Intelligence Devices, Systems, and Industrial Applications (EAI)

#### Low-Power Analog In-memory Computing Neuromorphic Circuits

#### <u>Roland Müller</u>, Bijoy Kundu, Elmar Herzer, Claudia Schuhmann and Loreto Mateu

19 September 2022 Milan, Italy

#### **Presentation Outline**

Introduction

- Design and Implementation

- DNN Top-Level

- Synapse Circuit

- Neuron Circuit

- Simulation Results

- Discussions and Conclusions

### Introduction

- Bring neural networks to edge devices requires

- High energy efficiency

- Low area

- Analog DNN accelerator a promising option but

- Accurate calculations and

- Robustness against PVT variations are challenging

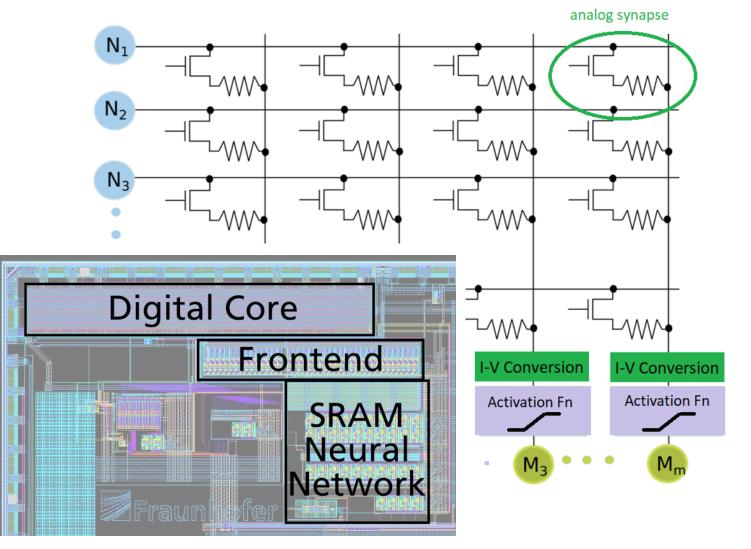

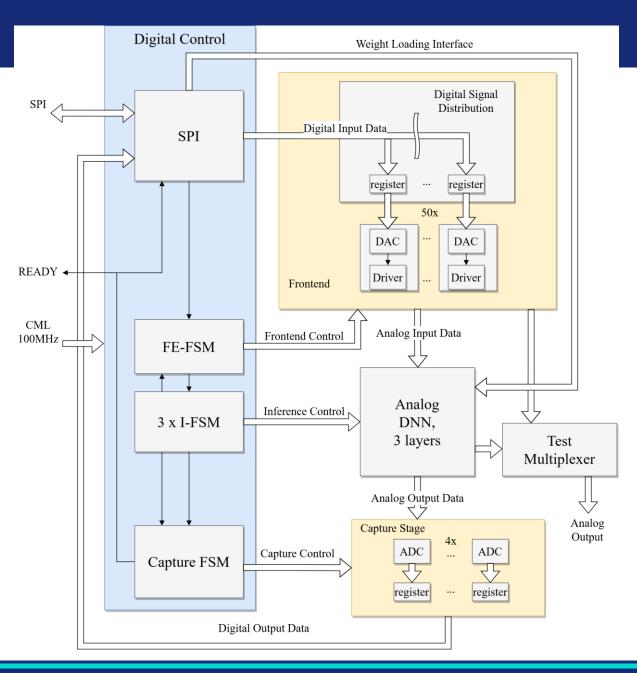

#### **DNN Top-Level**

- Digital control

- Communication via SPI

- DNN timing with FSMs

- Frontend

- Digital-to-analog conversion

- Driver stage for resistive DNN load

- 3-layer DNN

- SRAM based synaptic weight storage

- Fully connected

- 50x20, 20x10, 10x4

- Capture stage

- Analog-to-digital conversion

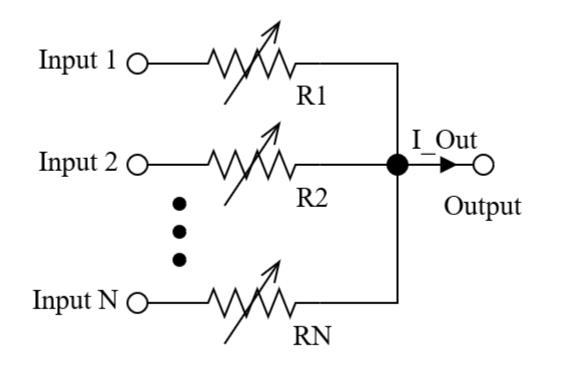

#### Synapse Circuit: State-of-the-Art

- Variable resistors to implement the weights

- V-I conversion

- Output node must be constant (virtual ground)

- Transimpedance amplifier

- Shunt resistor

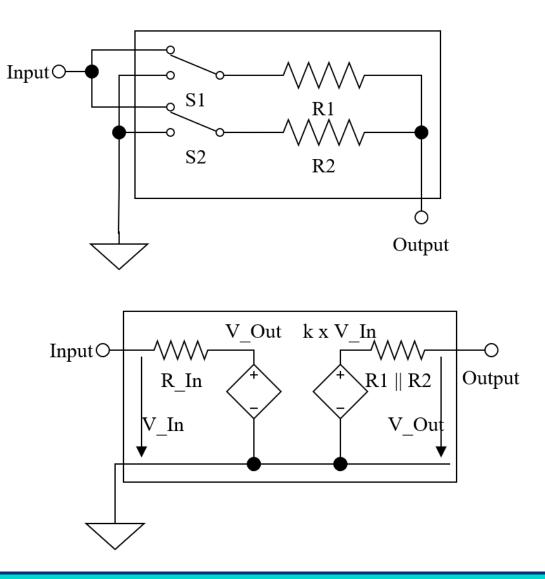

#### Synapse Circuit: Voltage Divider Approach

- Constant output resistance

- No virtual ground required

$$V_{OUT} = \frac{1}{N} \sum_{i=1}^{N} V_{In,i} \cdot k_i$$

→ Average operation

→ Gain required

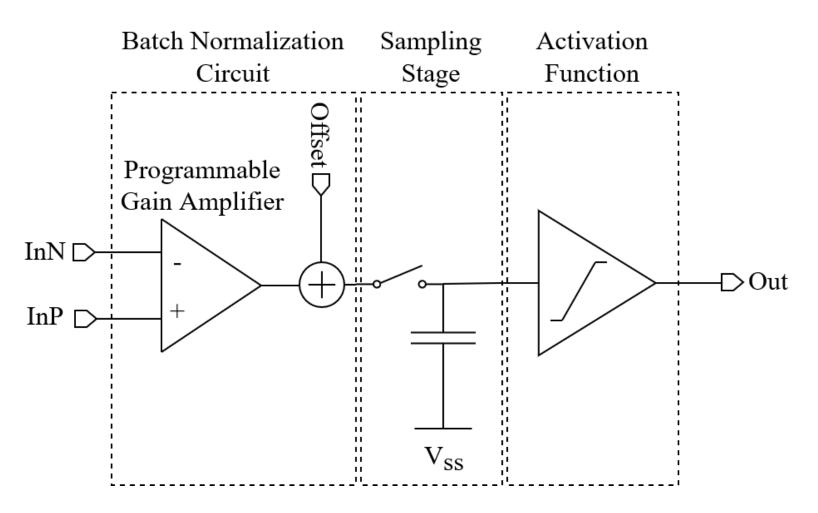

#### **Neuron Circuit**

- Batch normalization circuit

- Programmable gain

- Offset addition

- Sampling stage

- Non-linear activation function

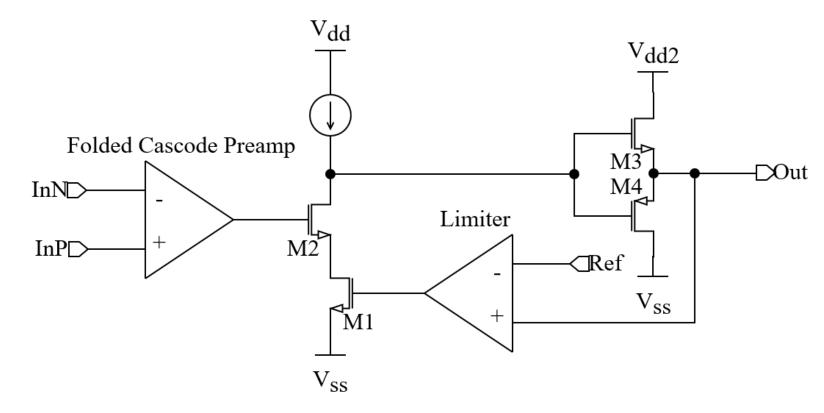

### **Neuron Circuit – Activation Function**

- Rectified Linear Unit

- Operational Amplifier

- Output range limited

- Upper limit: Supply Voltage

- Lower limit: Limiter

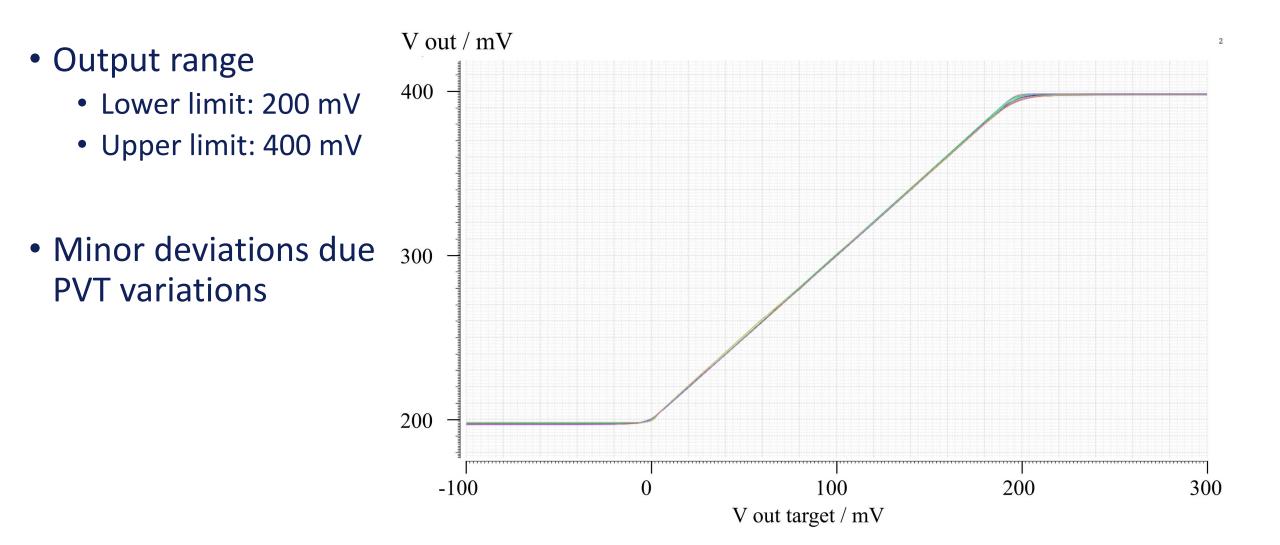

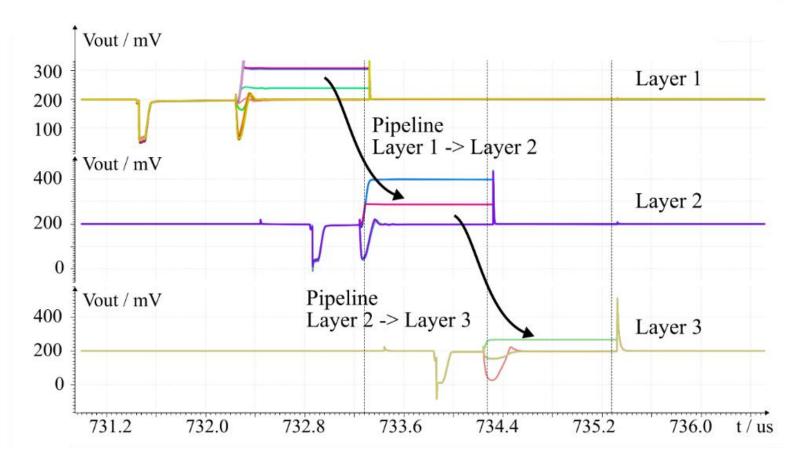

#### **Simulation Results**

10

| Parameter  | Value      |

|------------|------------|

| Average    | 1.9 mV     |

| Deviation  |            |

| Maximum    | 6.9 mV     |

| Deviation  |            |

| Energy/    | 9 nJ       |

| Inference  |            |

| Latency    | 5 μs       |

| Power      | 276 GOPS/W |

| Efficiency |            |

- Accurate DNN computations even with PVT variations due to synaptic circuit based on a voltage divider approach and robust neuron circuit

- Proof-of-concept simulation results show

- Functionality of the in-memory computation approach

- Low energy consumption

- Low latency

- Test strategy with test patterns for functional verification, evaluation and KPI measurement has been developed

- Evaluation and verification through measurement still pending

#### **Event Organisers**

The Key Digital Technologies Joint Undertaking - the Public-Private Partnership for research, development and innovation – funds projects for assuring worldclass expertise in these key enabling technologies, essential for Europe's competitive leadership in the era of the digital economy. KDT JU is the successor to the ECSEL JU programme. <u>www.kdt-ju.europa.eu</u>

The AI4DI project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826060. The JU receives support from the European Union's Horizon 2020 research and innovation programme and the national authorities. <u>www.ai4di.eu</u>

The TEMPO project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826655. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Belgium, France, Germany, The Netherlands, Switzerland. <u>www.tempo-ecsel.eu</u>. TEMPO has also received funding from the German Federal Ministry of Education and Research (BMBF) under Grant No. 16ESE0405. The authors are responsible for the content of this publication.

The ANDANTE project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 876925. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Belgium, France, Germany, The Netherlands, Portugal, Spain, Switzerland. <u>www.andante-ai.eu</u>

# Thank You For your attention

Copyright © 2022