# The International Workshop on Edge Artificial Intelligence for Industrial Applications (EAI4IA)

ANDANT

ECSEL JU

Vienna, Austria 25-26 July 2022 The International Workshop on Edge Artificial Intelligence for Industrial Applications (EAI4IA)

#### Deploying a Convolutional Neural Network on Edge MCU and Neuromorphic Hardware Platforms

<u>Simon Narduzzi</u>, CSEM, Switzerland Dorvan Favre, CSEM, Switzerland Nuria Pazos Escudero, Haute—Ecole Arc, Switzerland L. Andrea Dunbar, CSEM, Switzerland

Vienna, Austria 25-26 July 2022

# Edge computing

Edge processing is a significant target in Machine Learning

- Embedded ML: autonomous cars, drones, IoT, wearables...

- Reduced workload on servers

- Carbon footprint

Efforts from research and industry:

- Growth of interest: TinyML Community

- ANDANTE, TEMPO, AI4DI, ...

Edge ML is still challenging...

• What are the barriers?

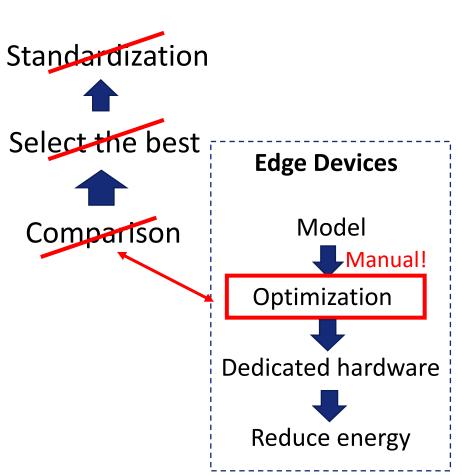

## Standardization of Edge Devices

Massive acceptance of Deep Learning due to standardization of tools

- The standardization of devices requires selection of the "best" one

- Selection = Comparison of devices

- Lack of standard deployment tools

- Lack of optimization standards

- Lack of automated tools

- Variability of device memory, ISA, compute capability...

- Lack of baseline performance (absolute? relative?)

## What has been done in the field yet?

#### Comparison

- TinyMLPerf : Benchmarks algorithms for (a few) Tiny devices

- Ostrau et al., 2020: Benchmarking for event-based processors

#### Deployment

- Heim et al. 2021, Falbo et al. 2019, Sanchez-Iborra et al. 2020:

- Intra-processor comparison

- Cortex-M processors

- STM32 processors

- Osman et al., 2022:

- CNN on Arduino Nano BLE and STM32 NUCLEO-F401RE

#### Our work

*Tomorrow*: "Benchmarking Neuromorphic

Computing for Inference" by Loreto Mateu

#### Our work

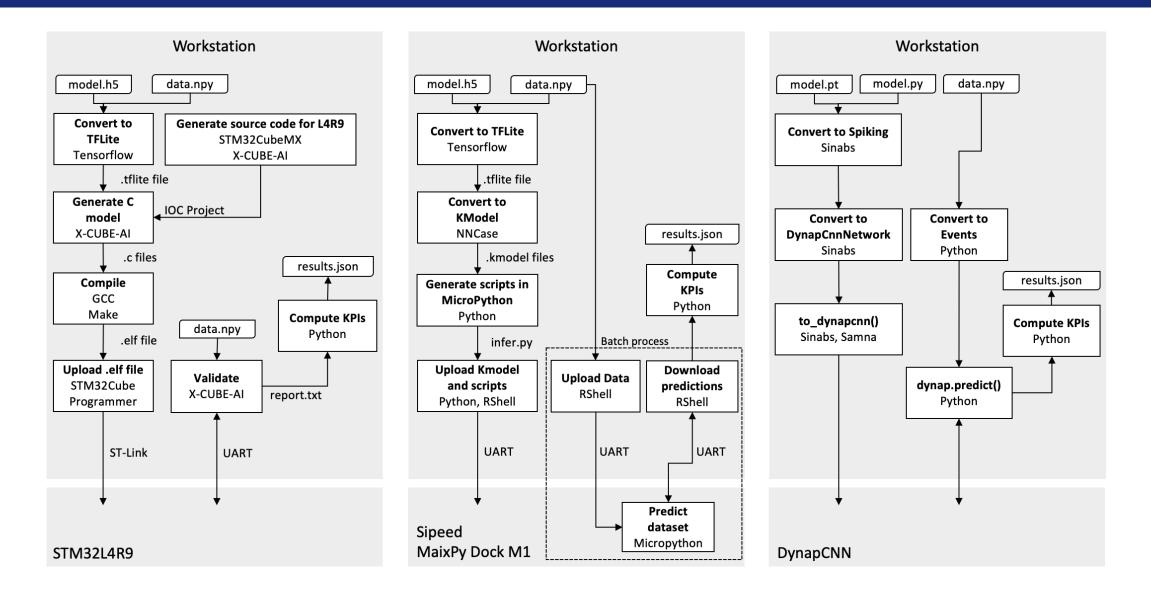

- Inter-processor comparison

- Automated deployment pipeline

- Open-source tool

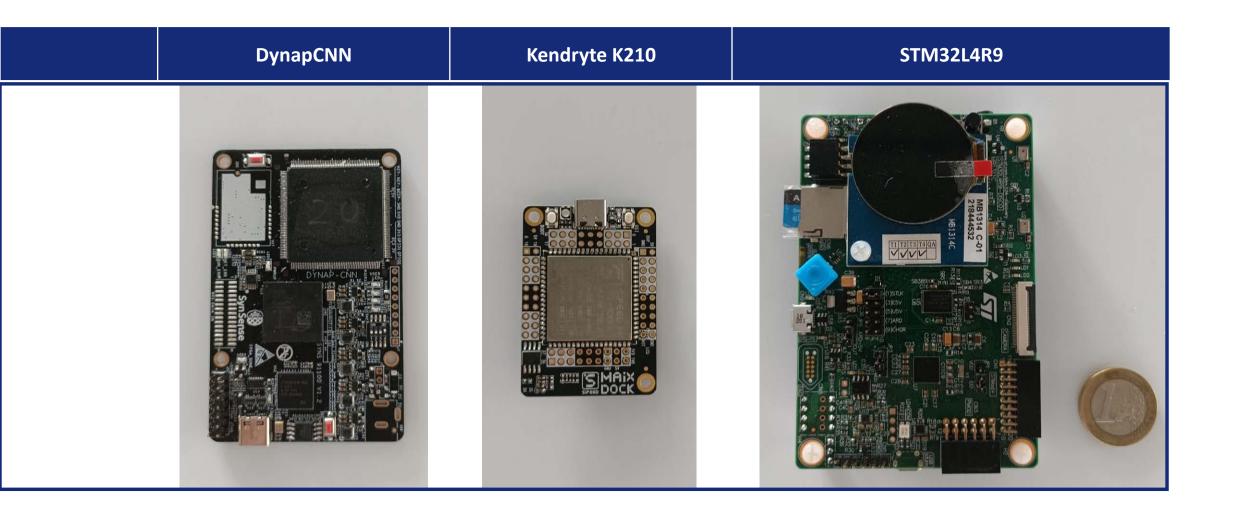

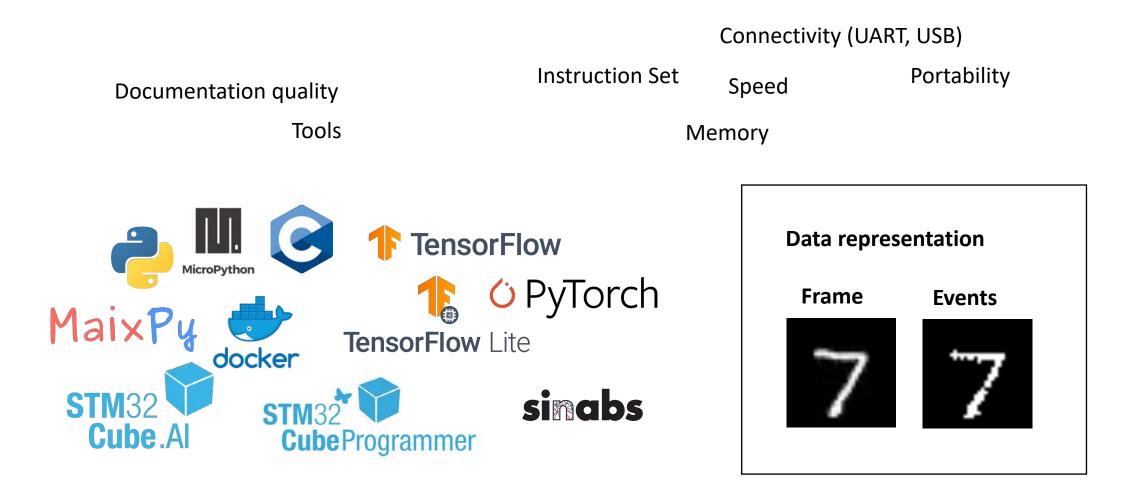

## Experimental setup: Board

# Experimental setup: Board

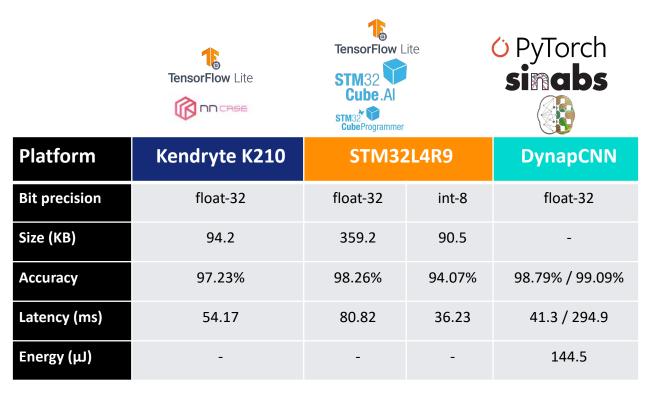

|             | DynapCNN     | Kendryte K210        | STM32L4R9     |

|-------------|--------------|----------------------|---------------|

| ISA         | Event-based  | Dual-core RISC-V 64b | ARM Cortex-M4 |

| Power       | 1mW          | 300mW                | 66mW          |

| Max Freq    | -            | 900 MHz              | 120 MHz       |

| TOPS/W      | -            | 3.3                  | -             |

| Standalone  | X            | $\checkmark$         | $\checkmark$  |

| Event-Based | $\checkmark$ | X                    | X             |

| Language    | Python       | MicroPython          | С             |

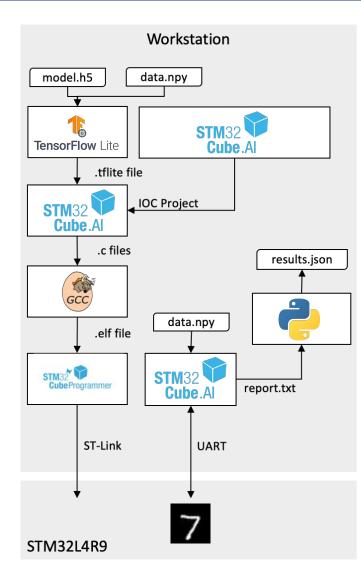

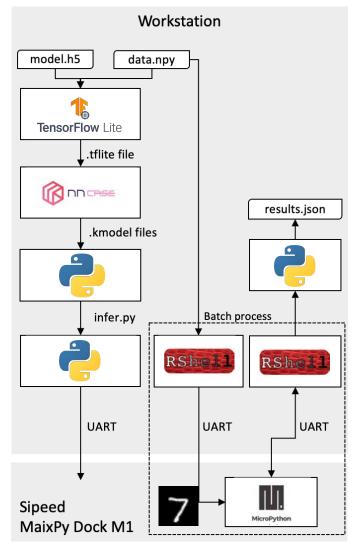

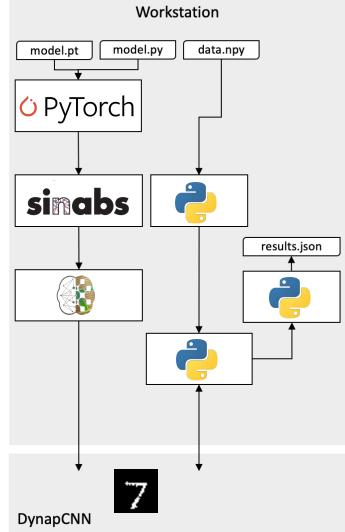

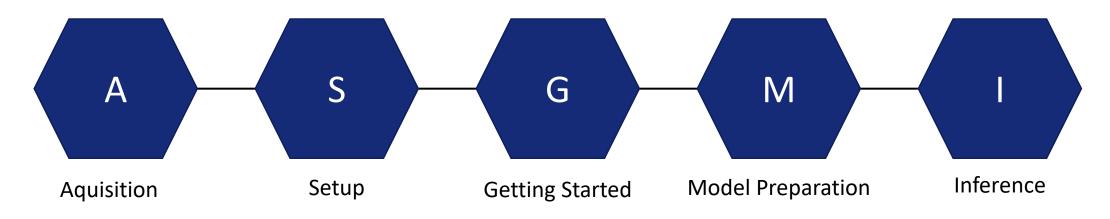

### **Deployment Pipelines**

# Deployment Pipelines (illustrated)

### Implementation: challenges

#### Network Architecture

#### LeNet-5 Architecture

"Gradient-based learning applied to document recognition", LeCun et al., 1998

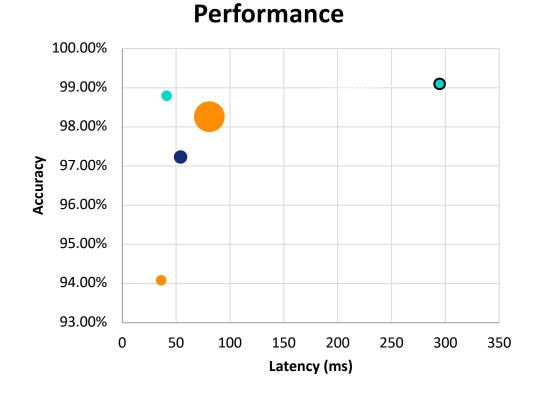

#### **Deployment Results**

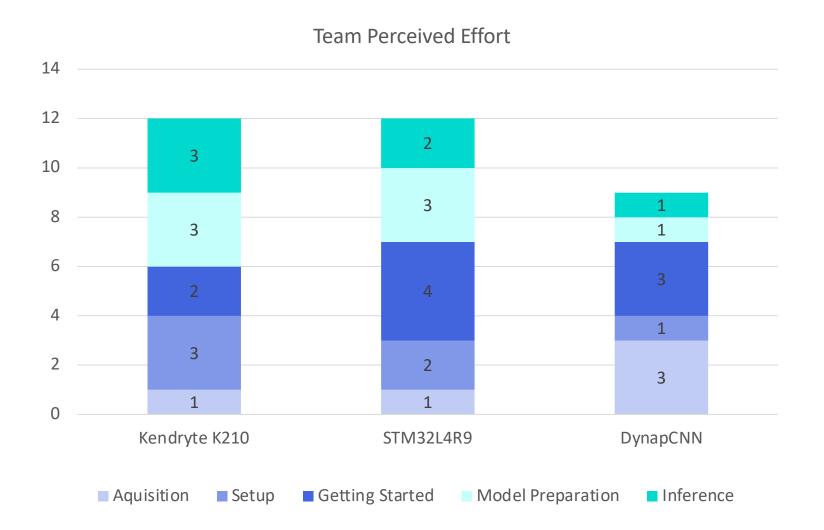

### Ease of Deployment

Scale:

1: Straight forward (script, command...)

5: Need constructor support

## **Deployment Results**

#### Conclusion and Outlook

#### Conclusion

- Automated the deployment on 3 constructors

- Provided a framework to evaluate the effort

- Comparison is still a challenge

#### Outlook

- Extend the support of devices

- Release the code as library

- Develop testbenches

- Define the KPIs (Hard and Soft)

- Validate / Improve the usability measure

#### Simon Narduzzi

- <u>simon.narduzzi@csem.ch</u>

- <u>https://linkedin.com/in/narduzzi</u>

## **Event Organisers**

for research, development and innovation - funds projects for assuring worldclass expertise in these key enabling technologies, essential for Europe's competitive leadership in the era of the digital economy. KDT JU is the successor to the ECSEL JU programme. www.kdt-ju.europa.eu

The Key Digital Technologies Joint Undertaking - the Public-Private Partnership

The AI4DI project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826060. The JU receives support from the European Union's Horizon 2020 research and innovation programme and the national authorities. www.ai4di.eu

The TEMPO project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826655. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Belgium, France, Germany, The Netherlands, Switzerland, www.tempo-ecsel.eu

The ANDANTE project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 876925. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Belgium, France, Germany, The Netherlands, Portugal, Spain, Switzerland. www.andante-ai.eu

# Thank You For your attention

simon.narduzzi@csem.ch